|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

2007 г.

Современные внутренние шины – смена приоритетов!Максим ШишаТестовая лаборатория Ferra PCI

Вот уже более десяти лет PCI – шина для подключения периферийных устройств к материнской плате компьютера – находится внутри практически каждого компьютера и, даже несмотря на моральное устаревание и уже недостаточную пропускную способность, продолжает (пока ещё) оставаться основной шиной для подключения к системе внешних устройств. Тем не менее она неуклонно сдаёт позиции новой последовательной шине PCI-Express, о которой чуть ниже. В далёком 1991 году компания Intel представила первую спецификацию системной шины PCI – Peripheral Component Interconnect (дословно: взаимосвязь периферийных компонентов). А в 1993 году уже началось активное продвижение на рынок шины PCI 2.0, которая дала толчок увеличению числа ориентированных на неё продуктов и довольно быстро вытеснила изрядно устаревшие к тому времени шины ISA и EISA. Причины успеха PCI – это гораздо большая скорость и возможность динамического конфигурирования периферийных устройств, подключённых к PCI (чего не было в ISA), то есть распределения ресурсов между периферийными устройствами наиболее приемлемым в данный момент времени образом и без постороннего вмешательства. Основные тактико-технические характеристики PCI 2.0:

Вскоре PCI «взяли на вооружение» также платформы с процессорами Alpha, MIPS, PowerPC, SPARC и другие. Ещё большее распространение получил стандарт 2.2. Отличия PCI 2.2 от 2.0:

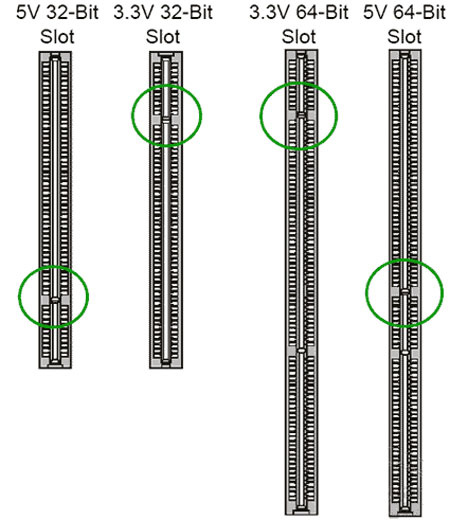

Типы PCI-разъёмов Со времён анонса PCI 2.0 разработкой и продвижением стандарта занимается специальная организация – консорциум PCI-SIG (Special Interest Group), она же занимается продвижением PCI Express. Существует множество вариаций на тему PCI 2.Х, наиболее распространённые из которых:

Эмблема PCI-X

Сводная таблица конструктивов карт и слотов в зависимости от версии стандарта

Однако, как и многие параллельные шинные решения (те же Parallel ATA, SCSI), шина PCI в данное время находится на границе разумного масштабирования производительности, после которого «гонка частот и разрядности» приведёт к непозволительно высоким технологическим усложнениям и, соответственно, к затратам. Но на данный момент проблема эффективной масштабируемости и наращивания уже решена, ведь в компьютерной индустрии уже полным ходом идёт переезд с PCI на новую последовательную шину PCI-Express.

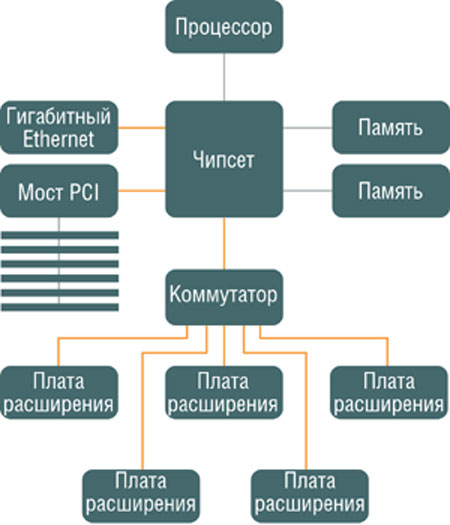

Различия топологий PCI и PCI-Express PCI-Express

Эмблема PCI Express Разработка рабочей группой Arapahoe, основанной компаниями Compaq, Dell, IBM, Intel и Microsoft при участии организации PCI-SIG, нового межкомпонентного интерфейса была начата фирмой Intel еще тогда, когда только ожидался выход в свет AGP 3.0 (он же AGP 8х). Так, программную модель PCI планировали унаследовать и в новом интерфейсе, чтобы системы и контроллеры могли быть доработаны для использования новой шины путём замены только физического уровня, без доработки программного обеспечения. Сам же интерфейс должен был быть последовательным. Это означало, во-первых, однозначное подключение «точка-точка», исключающее арбитраж шины и перетасовку ресурсов (как частный случай – прерываний). Во-вторых, упрощалась схемотехника, разводка и монтаж. В-третьих, экономилось место. Анонс первой базовой спецификации PCI-Express состоялся в июле 2002 года, когда уже стало ясно, что PCI-Express – это последовательный интерфейс, нацеленный на использование в качестве локальной шины и имеющий много общего с сетевой организацией обмена данными, в частности, топологию типа «звезда» и стек протоколов. Для взаимодействия с остальными узлами ПК, которые так или иначе обходятся собственными шинами, основной связующий компонент системной платы – Root Complex Hub (узел, являющийся перекрёстком процессорной шины, шины памяти и PCI-Express) – предусматривает систему мостов и свитчей. Логика всей структуры такова, что любые межкомпонентные соединения непременно оказываются построенными по принципу «точка-точка», свитчи-коммутаторы выполняют однозначную маршрутизацию пакета от отправителя к получателю. Соединение между двумя устройствами PCI Express называется link и состоит из одного (называемого 1x) или нескольких (2x, 4x, 8x, 12x, 16x и 32x) двунаправленных последовательных соединений lane. Каждое устройство должно поддерживать соединение 1x.

Таблица. Пропускная способность шины PCI Express с разным количеством связей В спецификации PCI-Express 2.0 планируется увеличить пропускную способность lane до 5 Гбит/с при сохранении совместимости с PCI-Express 1.1.

Использование шин и устройств PCI Express. Кроме всего прочего, PCI Express предлагает:

ИтогиКак мы видим, последовательные интерфейсы пришли в компьютерную индустрию всерьёз и надолго. Не за горами времена, когда такие почётные долгожители, как PCI, IDE(PATA), SCSI, совсем уйдут со сцены, ибо преемники – PCI Express, Serial ATA, Serial Attached SCSI – уже агрессивно отвоёвывают позиции у «старичков». В стане процессорных шин пока паритет – архитектура K8 компании AMD c организацией процессорной шины на основе HyperTransport уже зарекомендовала себя как удачное решение, но и компания Intel с «последней редакцией» параллельной шины FSB (QPB) чувствует себя довольно уверенно и не собирается от неё отказываться. Что касается возможной войны технологий PCI Express и HyperTransport, то здесь не тот случай – уж слишком разные сферы применения уготованы разработчиками этим решениям. Для вторжения в сферу сверхбыстрых передач у PCI Express недостаточно пропускной способности (максимум 8 ГБ/с для х16 против 41 ГБ/с у HyperTransport). Что касается работы HyperTransport с периферийными контроллерами, то данная шина не обладает для этого достаточными возможностями протоколов в силу своего изначального предназначения – замены процессорной шины, первое упоминание о «горячем» подключении появилось лишь в спецификации HyperTransport 3.0, да и стандартом пока что не предусмотрено внешних разъёмов.

|

|

CITForum © 1997–2025